# Automatic Bottle Filling Plant Controller using VHDL

Sayali Wayal<sup>#1</sup>, Pooja Kshirsagar<sup>#2</sup>, Gauri Pansare<sup>#3</sup>, Pratik Lokare<sup>#4</sup>, Raj Pisal<sup>#5</sup>, Rajveer Shastri<sup>#6</sup>

<sup>#</sup>Department of Electronics of Telecommunication, VPKBIET Baramati, Savitraibai Phule Pune University, Maharashtra, India.

Date of Submission: 25-06-2023Date of Acceptance: 07-07-2023

#### ABSTRACT

task

In this paper, we present a research project ondesigninganautomaticbottlefillingplantcontroller VHDL using code. The controller isdesignedtoautomatetheprocessoffillingbottleswith specified quantity of liquid. The а projectaimstoincreaseefficiency, reducewaste, and eli minate errors in the filling process.VHDLcode is program used to а field programmablegatearray(FPGA). The systemistested and simulated using VIVADOs of tware, and the resultsshow that the system is able to fill bottlesaccurately and efficiently.

**Keywords:** Automatic Bottle Filling Plant,VHDL Code, Basys3 (FPGA Board), VivadoSoftware.

#### I. INTRODUCTION:

The efficient filling of bottles is a crucial

invarious industries, including beverage, pharmaceuti cal,andchemical.Toautomatetheprocessandensureac curacy, automatic bottle filling controllers have been developed. In this researchpaper, we aim to design and implementanauto maticbottle filling controller using VHDL, a hardwaredescriptionlanguagecommonlyusedindigit alcircuitdesign.OurprojectinvolvestheuseofVHDL to create a digital circuit that controls thefilling of bottles based on input parameters such asvolume speed. The goal of this project is and toprovideareliable,accurate,andcosteffectivesolution fortheautomaticfilling ofbottles.

Theprimaryobjectiveofthis proje

Theprimaryobjectiveofthis project istodesignandimplement areliable,accurate,andcosteffectivesolutionfortheautomaticfilling ofbottles.Indoingso.

wehopetoprovideasolutionthatcanbeeasilyimpleme ntedinvariousindustries

andcanimprovetheefficiencyandaccuracy ofthefilling process.

TheuseofFPGA will enable us to create a digital circuit that

isflexible,scalable,andcanbeeasilymodifiedtomeetth especificrequirements of different applications.

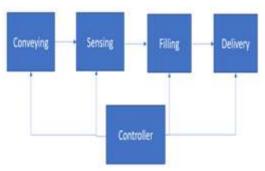

Fig1.1BlockDiagramofautomaticbottlefillingcontro ller.

Fig.1.1 shows the block diagram of states in automatic bottle filling plant controller. There are four states in this diagram i.e conveying, sensing, filling and delivering. All that's process are controlled by the controller as shown in fig.1.1. **2. Operations:**

The operation of an Automatic Bottle Filling PlantControllertypicallyinvolvesthefollowingsteps:

- 1. BottleDetection:Thesystemdetectsthepresenceo f a bottle using a sensor. If a bottle is present, thesystemproceeds tothenextstep.

- 2 Liquid Level Detection: The system detects the urrent level of liquid in the bottle using a sensor.

If the liquid level is below the desired level, the system proceeds to the next step.

2. Valve Opening: The system opens the valve toallow the liquid to flow into the bottle.

- 3. Liquid Filling: The liquid flows into the bottleuntiltheliquidlevelreachesthedesiredlevel. During this process, the system monitors the liquidlevelto preventoverfilling.

- 4. Valve Closing: Once the desired liquid level isreached, the system closes the valve to stop the flo wofliquid.

- 5. Bottle Removal: The system detects the removalof the filled bottle and waits for the next bottle to bedetected.

Throughout the operation, the system continuouslymonitors the filling process to detect any errors orabnormalities. If an error is detected, the

systemstopstheoperationandalertstheoperator.Thesa fety features of the system prevent overfilling oranyotherhazards.Theentireoperationiscontrolledb y the microcontroller, which is programmed usingVHDL code. The VHDL code defines the behaviorof the system and its interactions with the sensors,actuators,andothercomponents.

## II. FINITE STATE MACHINE (FSM):

Afinitestatemachine(sometimescalledafinit estateautomaton)isa

computationmodelthatcanbeimplemented withhard wareorsoftwareandcanbeused to simulate sequential logicand some computer programs. Finite state automat agenerate regular languages. Finite state machine scanb eused to model

problemsinmanyfieldsincludingmathematics,artifici alintelligence,games,andlinguistics.

TherearetwotypesofStatemachines:

- 1. MealyMachine

- 2. MooreMachine

#### 2.1 Mealy Machine:

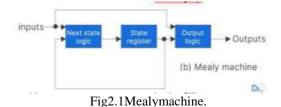

Inmealymachineoutputdependsbothuponth epresent state and the present input. The value of theoutputfunctionisafunctionofthetransitions and the changes, when the input logic on the present state is done. Mealy outputs are asynchronous. T hey can change immediately with input change, indepen dent of the clock as shown in fig 2.1.

#### 2.2 Moore Machine:

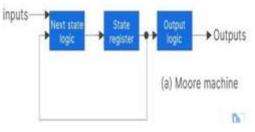

In Moore machine output depends only on thepresentstate. The value of the output function is a function of the current state and the changes at the clockedges, whenever state changes occur. as shown in fig 2.2.

Fig2.2Mooremachine.

## III. RELATED WORK:

- 1. AutomaticbottlefillingsystemsusingPLC:Progr ammablelogiccontrollers(PLCs)havebeenwidel yusedforautomationinvariousindustries, bottle including filling. PLCbasedautomaticbottlefillingsystemshavebeende veloped and implemented, which use sensorsandactuatorstocontrolthefillingprocess. These systems have been found to be reliable.accurate.and efficient.

- Automaticbottlefillingsystemsusingmicrocontr 2. ollers:MicrocontrollerssuchasArduinohave alsobeenused forautomatingbottlefilling. Thesesystems usesensors and actuators, and the microcontrolleris program med to control the filling process basedon the input parameters. These systems havebeenfoundtobecosteffectiveandeasytoimplement.Automaticbottlef illingsystemsusingLabVIEW:LabVIEWisagrap hicalprogramminglanguageusedforautomationa nddataacquisition.Ithasbeenusedtodevelop automaticbottlefillingsystems, where LabVIEW is used to control the filling processand monitor the system. These systems offer auserfriendly interface and real-time monitoringcapabilities.

- 3. Research on sensors for bottle filling: Sensorsplay a crucial role in the automatic bottle fillingprocess, as they are used to measure the volumeofliquidandregulatetheflow.Therehaveb eenvariousstudiesonthedevelopmentandevaluat ionofsensorsforbottlefilling,includingultrasonic ,capacitive,andopticalsensors.Thesearesomeex amplesofrelatedworkinthe

- 4. areaofautomaticbottlefillingcontroller

| Parameters          | Programmable<br>Logic controller               | Field<br>Programmable<br>Gate Array                         |    |  |  |

|---------------------|------------------------------------------------|-------------------------------------------------------------|----|--|--|

| Purpose             | Industrial control<br>and automation           | General-purpose<br>programmable<br>device.                  |    |  |  |

| Functionality       | Sequential and<br>logic-based<br>control tasks | Custom digital log<br>and algorithms.                       | ic |  |  |

| Programming         | industrial-specific<br>languages.              | Hardware description<br>languages like<br>VHDL or Verilog.  |    |  |  |

| Power<br>Efficiency | Power loss is more than FPGA                   | Power optimization<br>based on application<br>requirements. |    |  |  |

# **IV. IMPLEMENTATION:**

In our research paper a state machine diagram is designed for the desired state machine which

cancontrolthewholebottlefillingprocessautomaticall The system requirements include v. theinputsignals from the liquid level sensors, the output signals to control the valves and pumps, andthe processing blocks required to calculate the flowrate of the liquid. the system is able to detect when he bottle is full and stop the filling process. TheVHDL architecture for the system will consist ofinput, output, and processing modules. The inputmodule will responsible for be receiving the signals from thesensors, the processing module will cal culate the flow rate and control the valves, and the output module will control the signal stost op the filling process when the bottle is full. And so on forremainingstateslikecapping, labelling, qualitychec kingand packaging.

The VHDL code will be written for each module, including the input, processing, and output mo dules. The VHDL code will be verified using simulations of tware to ensure that it is functioning

correctly.The simulation software will provide a waveformthatshowstheinputandoutputsignalsofthed igitalcircuit.Byanalysingthewaveform,thedesignerc anverifythattheVHDLcodeisperformingtherequired calculationsandproducingthecorrectoutput signals.After verifying the VHDL code, thenext stepistosynthesizetheVHDLcode.Thisinvolves translating the VHDL code into a gate-level netlist, which describes the logic gates andtheirinterconnectionsrequiredtoimplementthedi gitalcircuiton theFPGA.

Once the VHDL code is synthesized, the next

stepistoplaceandroutethedesign. Thisinvolvesmappi ng the logic gates onto the FPGA and routingthe connections between them. Finally, the FPGA can be programmed with the synthesized designa nd the system can be tested to ensure that it meets the system requirements. If any issues are found, the VHDL code can be modified and the synthesis and placeandroutesteps can be repeated until the design is functioning correctly.

| Name  | Direction | Description             |

|-------|-----------|-------------------------|

| clk   | INPUT     | Usedto giveclocksignal. |

| reset | INPUT     | UsedtoResetthesystem    |

| remptybottl                                  |  |

|----------------------------------------------|--|

| Usedtocheckwhetherbottleis<br>filled ornot   |  |

| rbottleisper                                 |  |

| Usedtocheckqualityoffilled&L<br>belledbottle |  |

| ekaging                                      |  |

| es.                                          |  |

|                                              |  |

|                                              |  |

| es.                                          |  |

| ting                                         |  |

| e<br>s                                       |  |

Table1.Input/Outputswithremarks.

# 4.1 Field Programming Gate Array(FPGA)

A field-programmable gate array (FPGA) is asemiconductordevicethatcanbeconfiguredbythe designer after manufacture, hence the name"fieldprogrammable".FPGAsareprogrammedusingalogicc ircuitdiagramorhardwaredescription language (HDL) source code. Thisprogram is reprogrammable bv the designer ifnecessary.IftheFPGAisprogrammedbythe user, the user can also modify or change theprogram.TheimplementedprogramintheFPGA the operation of the chip shows or kit. They can be used to implementary logic function that an application-specific integrated circuit (ASIC) might perform, but the ability toupdatefunctionalityafterdeliveryoffersadvantagesf ormanyapplications.FieldProgrammableGateArrays (FPGAs)arewidelyused in rapid prototyping and proof of conceptdesign as well as in electronic systems

wherecustomICmaskmanufacturingisreallyexpensi ve due to small quantities. The systemwasimplementedinhardwareusingFPGABas ys 3. According to the design procedure, itstartswiththedescriptionofthecircuit, inwhich the whole circuit is designed by logic, which is done using (VHDL). A functional descri ption was then performed, followed bysynthesis and post-synthesis simulations. Thenthe implementation and time simulation takesplace and the generated file is downloaded tothe target device. This system used as а targetdeviceisanFPGAkit.Circuitdesignordescriptio can be done using VHDL n followedbyfunctionalsimulationandsynthesis.Thede flow is followed sign until timing simulationandthenthegeneratedfileisdownloadedtot hetargetdevice(FPGA).FPGAshavegainedrapidado ptionand growthover thepastdecadebecausethey canbeusedinaverywidevarietyof applications. A list of typical applicationsincludes: random logic, integration of multipleSPLDs, devices

# 4.2 Basys3 Board:

The Basys 3 is a versatile developmentboardthatprovidesahandsonlearningexperiencefordigitaldesignandFPGApro gramming. It offers a range of features

and capabilities to support project development and experimentation. The board's Xilinx Artix-

7FPGAisapowerfulprogrammablelogicdevicethat allows users to implement custom digitalcircuits.With33,280logiccells,1,800Kbitsofbl ockRAM,and90DSPslices,theFPGAprovidesampler esourcesforcomplexdesigns.

TheBasys3boardincludesvariousinput/output interfaces that enable interactionwiththeboardandexternaldevices.Thesein terfaces include user switches, LEDs, pushbuttons,seven-

segmentdisplays, VGAoutput, USB-

UARTbridge,andPmodconnectors.Thesefeaturesall owforuserinput,outputdisplay, and connection with peripherals. Fordata storage, the board provides 256 MB ofDDR3memory,whichcanbeusedtostoredataduring operation.Additionally,ithas16MBofQuad-SPI flash memory that allows for nonvolatilestorageofFPGAconfigurations,ensuringeasy reconfigurationof theFPGA.

Insummary,theBasys3boardisapopular choice for digital design and FPGA-based projects. Its Xilinx Artix-7 FPGA,

I/Ointerfaces, memory capabilities, educational resour ces, and expandability

makeitavaluabletoolforlearningandprototypingdigit alcircuitsandembeddedsystems.

FPGAs.

## V. DESIGN METHODOLOGY:

The system consists of a filling machine, aconveyorbelt, sensors, and an FPGAbased controller. The filling machine is used to fill the bottles with the liquid, and the conveyor beltisused to transport the bottles to the filling machine. Thesensors are used to detect the presence of

bottles ontheconveyorbeltandthelevelofliquidinthefillingm achine. The FPGA-based controller is responsiblefor controlling the filling machine, conveyor belt, and sensors.

TheVHDL codeisusedtoprogram theFPGA with the necessary control signals. The codeisdesignedtomonitorthesensors, control the conv eyor belt, and fill the bottles with the requiredamountofliquid.Thecodealsoincludeserrorh andling routines to detect and correct errors in thefilling process. Theprovided code represents thebehavioral description of a bottle filling controllerusingaFSMapproach.Itdefinesanentitycall ed`bottlefillingplantcontroller`withinputandoutputp ortsforvarious signals and control lines.Thearchitectureblockdescribes the behavior of the controller. Ituses a clock (`clk`) and a synchronous reset signal(`reset`) to control the state transitions and actionswithin theFSM.

Fig4.2 Basys3kit

TheBasys3isasmallcircuitboardthathelps people learn about digital logic designusing a technology called Field-ProgrammableGateArrays. It has a special chip called the Xilinx Artix-7 FPGA that can be programmed to perform different tasks. The board has buttons, switches, lights, and displays that you can use to interact with your circuit designs and see the results. It also has USB ports, a UART port, and an Ethernet port to connect to other devices like computers. To make the Basys 3 work, you use software called Vivado Design Suite or similar tools. These tools let you write and test your circuit designs, and then program the FPGA on the board. The Basys 3 is commonly used in schools and by hobbyists to learn about digital circuits and how to program

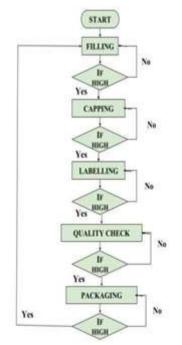

Fig5.1.Flowchartforautomaticbottlefillingcontroller

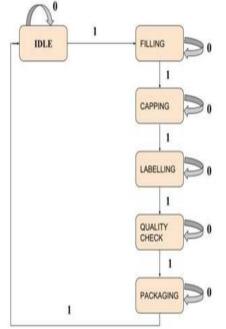

Fig. 5.1definesthedifferent states of the controller, including

IDLE,FILLING,CAPPING,LABELING,QUALIT Y\_CHK, and PACKEGING. The state signal represents the current state of the controllerand is initialized to IDLE during reset. Inside theprocessblock,theFSMisimplementedusinga case `statementbasedonthecurrentstate.Eachstatehasasso ciatedconditionsandactions:

## 5.2 Descriptionofstates:

**IDLEstate:**Thecontrollerwaitsforanemptybottletob edetected(`empty\_sensor='1').Whenan emptybottleisdetected,

theconveyorisactivated(`conveyor<='1``),andthecon trollertransitions to theFILLINGstate.

FILLINGstate: The valve is turned on (`valve

<= '1")to fill thebottleuntil itbecomesfull(`full\_sensor='1"). Oncethebottleis full, thevalveis turnedoff, theconveyoris activated,andthecontrollertransitionsto theCAPPINGstate.

CAPPINGstate.

**CAPPINGstate:**Thecapperisactivated(`capper<='1'`)tocheckandtightenthebottlecap.Whenthecapisdete cted(`cap\_sensor='1``),thecapperisturnedoff,thecon veyorisactivated,andthecontrollertransitions totheLABELINGstate.Thelabelleris alsoactivated(`labeller<='1``)inthis state.

Fig5.2.Statediagramforautomaticbottlefillingcontro ller.

LABELING state:Thelabel is appliedto thebottlewhen thelabelsensordetects thebottle(lable\_sensor='1").Afterlabelling,thelabele risturned off,theconveyorisactivated, andthecontrollertransitionstotheQUALITY\_CHKst ate.Thecheckingsignal(`cheking<='1")isactivatedin this state.

## QUALITY\_CHK

**state:**Thequalityofthefilledbottleischecked(`quality \_check='1``).Ifthequalitycheckpasses,thecheckingsi gnalisturnedoff,theconveyorisactivated,andthecontr ollertransitions tothePACKEGINGstate.

PACKAGINGstate: Thebottlesarepackaged(`packa ger<='1``).Oncepackagingiscompleted(`packaging done='1``),thepackageristurnedoff,theconveyorisact ivated, and the controller transitions back totheIDLEstatetowaitforthenextempty bottle. The code also includes default assignments for theoutput signals in the `others` state and during resettoensureproperinitializationanderrorhandling. In summary, the code implements a bottle fillingcontroller that FSM controls the filling, capping, labeling, quality checking, and packaging processes of the automatic bottle filling plant. The controllertransitionsbetweenstatesbasedonspecificc onditions and activates the necessary componentsto perform the corresponding actions at each stageofthebottlefilling process.

## VI. SIMULATION AND TESTING:

The system is tested and simulated usingVivado software. The simulation results show thatthesystemisabletofillbottlesaccuratelyandefficie ntly.Thesystemisabletodetectthepresenceof bottles conveyor belt, on the fill the bottles withthespecified amount of liquid, and transport thebottlesawayfromthefillingmachine. The system is a lso able to detect errors in the filling process andtakecorrectiveaction

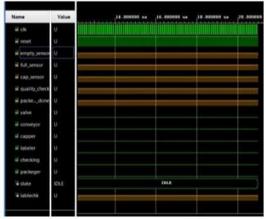

Fig5.1Simulationwaveform showingIdleState

The fig.5.1 shows the waveform of Idle State. When we give Clock signal and reset input to high the controller goes in Idle state all the outputs like Valve, Conveyor, capper etc. all goes Low (OFF) as per the VHDL code.

Fig5.2.SimulationwaveformshowingFillingState

The fig.5.2 shows the Simulation waveform of Filling State, When we give high input to empty bottle sensor (Empty bottle detected) then controller goes to Filling state, then Valve turns On (high) and filling of bottle starts.

Fig 5.3SimulationwaveformshowingCappingState

The fig. 5.3 shows the Simulation waveform of Capping State, When we give high input to the bottle filled sensor (bottle is filled) then Valve turns OFF and the controller goes to Capping state, then Capper turns On (high) and Capping of bottle starts.

Fig 5.4Simulationwaveform showing LabellingState

The fig.5.4 shows the Simulation waveform of Capping State When we give high input to the Capping sensor (bottle is capped) then capper turns OFF and the controller goes to Labelling state, then Labeler turns ON and Labelling of bottle starts as per program.

5Simulationwaveform showingQualityCheck State

The fig.5.5 shows the Simulation waveform of Capping State, When we give high input to the Labelling sensor (bottle is Labelled) then Labeler turns OFF and the controller goes to Quality Check state, then Quality Checking turns ON and Checking of bottle starts as per program.

Fig 5.6 .Simulationwaveform showingPackagingState

The fig.5.6 shows the Simulation waveform of Packaging State When we give high input to the Quality check sensor (bottle Quality is checked) then Quality Checking turns OFF and the controller goes to Packaging state, then Packager turns ON and Packaging of bottle starts.

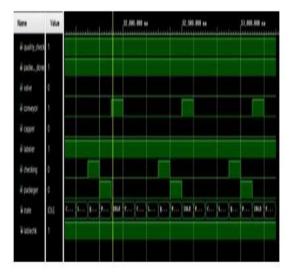

Fig 5.7. Simulation waveformForautomaticbottle filling Controller

The fig.5.7 shows the Simulation waveform of automatic bottle filling Controller, As per our VHDL

code controller shows the results from one state to another and so on, And this process achieves our aim to automate the bottle filling process by using FPGA.

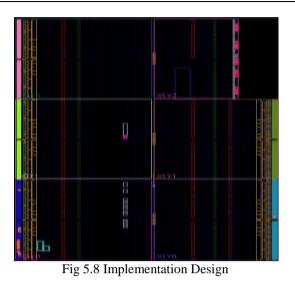

shows theImplementation Fig 5.8 Designof the automatic bottle filling plant controller Using VHDL language. The automatic bottle filling plant controller consists of sensing systems to detect bottles and measure liquid levels. It controls the conveyor system for bottle transport and synchronizes the filling mechanism. The controller employs algorithms for precise control, adjusts conveyor speed, and manages the overall operation. It includes a user-friendly interface for monitoring and control, and a central unit for processing signals and coordinating components. Safety features and data logging for analysis are also incorporated.

Fig.5.9 utilization graph

Above fig.5.9 is graph the utilization graph of the automatic bottle filling plant controller. An utilization graph represents resource allocation in a system over time. Designing an automatic bottle filling plant controller using VHDL involves identifying requirements, defining

architecture, writing VHDL code, simulating and verifying, synthesizing and implementing, and performing utilization analysis.Optimization techniques include resource sharing, pipeline design, parallelization, and code optimization. Utilization graphs can be generated using VHDL simulation or synthesis tools with utilization analysis capabilities.

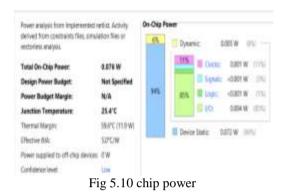

As we see in Fig 7.3, is a diagram is of chip power of FPGA. The chip power of an FPGA (Field-Programmable Gate Array) refers to the power consumption of the FPGA chip itself. It is an important consideration in FPGA design. Factors that influence chip power include the configuration of logic elements, memory elements, interconnects, and I/O interfaces. Power consumption can vary based on the specific FPGA model, the configuration of thedesign, and the operating conditions. Designers aim to optimize power usage through techniques such as power gating, clock gating, and voltage scaling. Power reports estimation tools andare available to analyze and optimize chip power in FPGA designs.

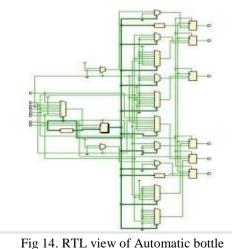

TheRTLviewofthemachineisshowninfigure 5.8

fillingController.

# VII. CONCLUSION:

The present FPGA based automatic bottle fillingcontroller is implemented using FSMs with the helpofXilinxVivado.Thedesignisverifiedon theFPGA Basys 3 development Board. The VHDLbaseddesignprovidesaflexibleandscalablesolution that can be easily adapted to different typesof liquids and bottle sizes, making it applicable invarious industries. By utilizing a state diagram and appropriate input and output modules, the systemcan accurately detect and control the filling process, ensuring that each bottle is filled to the desired le vel. .The verification and synthesis of the VHDL code,followedbytheplacementandroutingofthedesig nontotheFPGA, enable the system to be implemented a ndprogrammedeffectively.Thesimulation process ensures the correct functionalityofthesystem, while the FPGA implement ationallows forreal-world testingandvalidation.Overall,theimplementationofth eAutomaticBottleFillingControllerusingVHDLdem onstratesthepotential of digital circuit design and automation

inenhancingindustrialprocesses. The successful integr ation of hardware and software components paves the way for improved efficiency, accuracy, and productivity in bottle filling operations, making it avaluable contribution to the field.

## **REFERENCES:**

- Smith,A.,&Johnson,B.(2022).Real-TimeControlSystemforAutomatedBottleFi llingUsing FPGA. International Journal of AdvancedResearchinElectronicsandComm unicationEngineering, 9(2),145-152.

- [2]. Gupta,R.,&Sharma,S.(2021).Design andImplementationofAutomaticBottleFilli ngSystem using VHDL and FPGA. Proceedings oftheInternationalConferenceonSignalProc essing,Communication,andNetworking.

- [3]. Patel,K.,&Shah,P.(2020).FPGA-BasedBottleFillingControlSystemusingPI DController.JournalofElectricalEngineerin gand Automation,7(4),231-240.

- [4]. Anderson, M., & Wilson, L. (2019). Comparat iveAnalysisofAutomaticBottleFillingContr ollers: A Review. International Journal of Control Systems and Robotics, 6(3), 87-98.

- [5]. Johnson, C., & Davis, R. (2018). Implementat ionofaBottleFillingControlSystemusingV HDLandFPGA.IEEETransactionsonIndust rialElectronics, 65(9), 7154-7162

- [6]. "DesignofAutomaticBottleFillingSystemB ased on FPGA" by Junjie Li, Yonghua Li, andXuewu Liu, published in the Journal of

AppliedMathematics,StatisticsandInforma tics,Vol.15, No. 2, 2019.

[7]. "DesignandImplementationofAutomaticLi quid Filling System Based on VHDL" by J.J.Tian, Q.H. Xu, and Y. Jiang, published in

theProceedingsofthe2017InternationalCon ferenceonComputer,NetworkandCommuni cation Engineering.

- [8]. "DesignandImplementationofAutomaticB ottle Filling and Capping Machine Using PLCandVHDL"byV.K.GuptaandP.Prasad, publishedintheInternationalJournalofEngin eering Research and Technology, Vol. 3,No. 3, 2014.

- [9]. "DesignandImplementationofAutomaticLi quidFillingSystemUsingVHDL"byN.Ahm edandM.Ahsan,publishedintheProceedings ofthe2013InternationalConferenceonElectr icalEngineeringandInformationCommunic ationTechnology.

- [10]. "Automatic Bottle Filling System Using VHDL"byS.Singh,A.Kumar,andR.Kumar, publishedintheInternationalJournalofAdva ncedResearch in Computer Science and ElectronicsEngineering,Vol.1,Issue4,2012